Automatic Placement and Routing

Constraint Driven Automatic Place and Route System

SX-Meister ACC

Automated design environment that complies with design constraints for analog ICs

Realizes layout automation with procedures that follow the designer’s way of thinking,

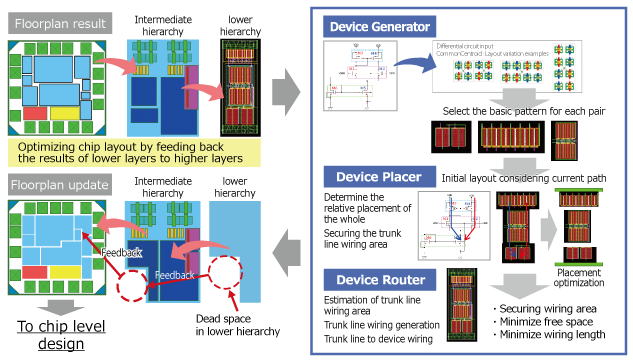

■Main features of chip-level design

- Automatic placement function that enables early determination of the optimal proaplan

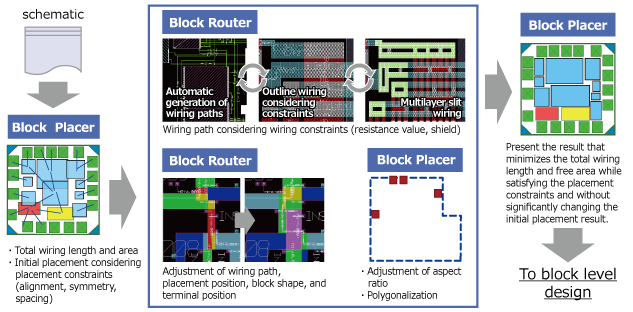

- Constraint-driven router that automatically determines the wiring area and shape according to wiring constraints

- Automatic placement of soft block ports at the nearest routing points

■Main features of block-level design

- Easy and high quality generation of pair placement and wiring using basic patterns

- Initial placement considering current path, device type, etc., and placement optimization function that secures an appropriate wiring area for the initial placement.

- Automatic wiring function using a wiring generation method that requires as little manual modification as possible.

Download

Download