回路設計

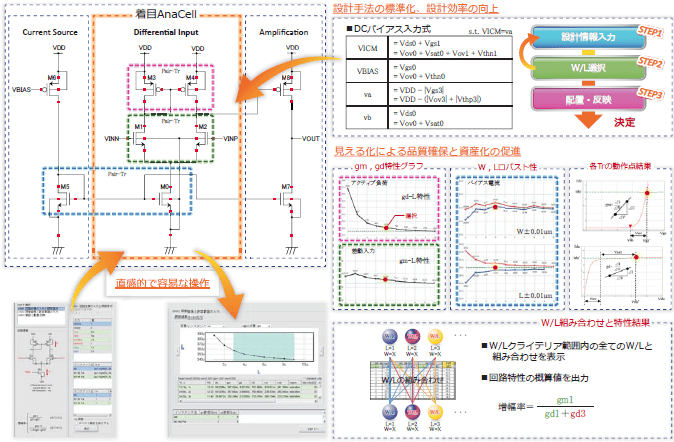

革新的なセルベース(AnaCell)のアナログ回路設計手法を実現

■特長

プロセスフリーなセルベース設計による生産性の向上

- バイアス設計のイタレーション作業を効率化

- ロバスト性を考慮した設計手法による品質確保

- 設計手法を標準化し再利用を促進

統合回路設計システム

SX-Meister Asca-Advanced

■セルベース設計(AnaCell)の特長 (特許第6568980号)

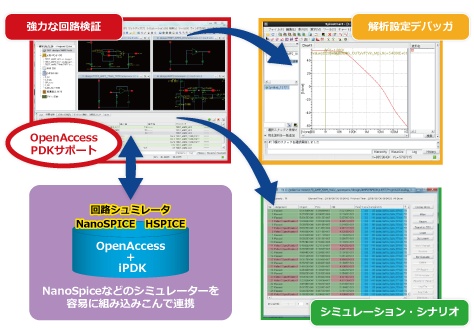

■ 回路設計(Asca-Advanced)の基本機能

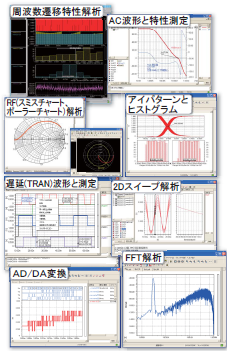

シミュレーション波形解析

SX-Meister SpiceChart

業界トップクラスの大規模データ表示スピード

直感的な操作でストレスなく解析

- ポストレイアウトシミュレーション規模の波形を超高速に表示

5ギガバイトオーダを1分で表示 - Drag & Dropとクリック操作だけでコマンド実行

- 資料作成支援

日本語コメント入力、測定値のコピー&ペースト - 豊富な測定機能

マルチタブによる複数解析の同時表示

ジッタ解析、ヒストグラム表示

EyeDiagram, AD/DA変換 - 見やすい表示

XYカーソル、点カーソルによる測定結果表示

測定値色、背景色のカスタマイズ - 各種フォーマットに対応

tr0/ac0/dc0, fsdb, raw, psf, csv

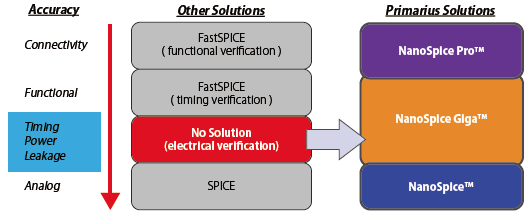

全ての領域をカバー可能な大規模かつ高速な回路シミュレータ

NanoSpiceTM

NanoSpice GigaTM

NanoSpice ProTM

■ NanoSpiceTMの特長

- 高精度:アナログ回路の精度を満たすPure SPICEエンジンを搭載

- 5倍以上の大容量: >50M 素子のシミュレーションが可能

- 高速並列SPICE:従来SPICEより高速化

- 互換性:従来SPICEの入出力ファイル互換

- 先端プロセス対応:14/7/5nm FinFET対応

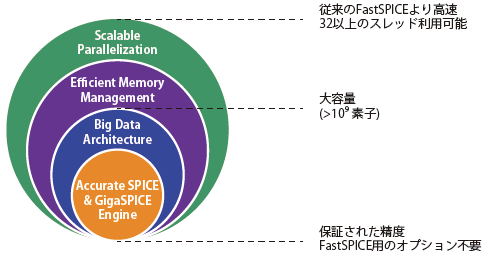

■NanoSpice GigaTMの特長

- Pure SPICEエンジンを搭載した NanoSpice GigaTM は、従来のFastSPICEでは対応できない、大容量で高精度のシミュレーションを可能にします

■NanoSpice ProTMの特長

- FastSPICEアルゴリズムの革新により、回路のトポロジー認識と自動分割が可能に

- NanoSpice GigaTMよりもさらに大容量で、10倍以上の高速化

- ADS(Adaptive dual-solver)により、アナログ回路の精度とデジタル回路の高速動作を確保

■NanoSpiceTM/NanoSpice ProTM/NanoSpice GigaTMの適用分野

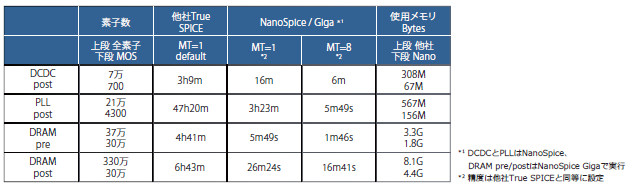

■実行速度 例

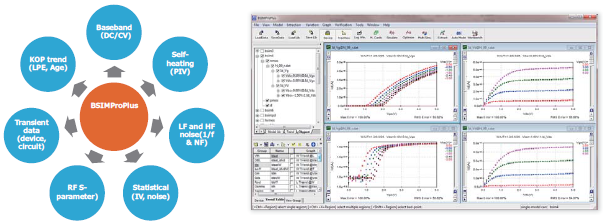

SPICE モデルパラメータ抽出・最適化ツール

BSIMProPlus

■業界標準のデバイスモデルパラメータ抽出ツール

- 全世界で100を越えるユーザ企業

- Bulk/SOI/FinFET/BJT/HBT/LDMOS/TFT, 16/14nm, 10/7nmに対応

- サポート対象モデル: BSIM3, BSIM4, BSIM6, BSIM-CMG, BSIM-IMG, BSIMSOI, UTSOI, HiSIM2,HiSIM_HV, PSP, GP-BJT, RPI TFTなど

- 多様なモデル用途: Baseband, RF, Noise, Statistical/corner, Reliability, LDE

■主な機能

- 測定器を制御してのデータ測定・取得

- パラメータ⾃動抽出/最適化/マニュアルチューニング

- Re-targeting, Bin model tuning

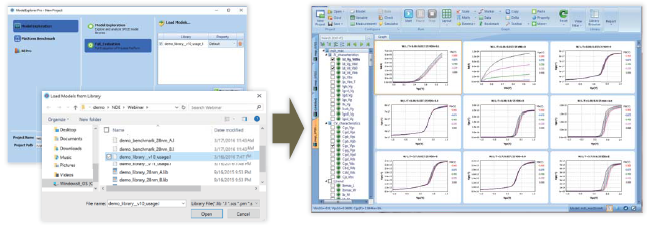

PDK/SPICE モデルライブラリ評価・管理ツール

ME-Pro

PDK ライブラリを入力として,デバイスモデルを解析・比較・検証することで テクノロジ・PDKの評価・ベンチマークが可能

- Library Browser でモデルライブラリの構成・内容を確認

- あらかじめ設定した内容をもつテンプレートに沿ってグラフィカルにモデル・デバイスのふるまいを表示

- 解析メニューをGUI から選ぶことで,スクリプトを組むことなく設定

- 解析内容をレポートドキュメントに出力

デバイス雑音測定・モデルパラメータ抽出ツール

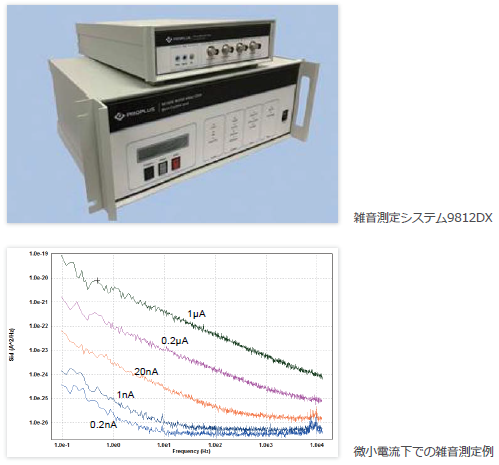

NoiseProPlus/9812DX

9812DX:

全世界で100社以上が採用している業界のデファクトスタンダード 9812シリーズの最新機種

従来機9812Dシステムを、測定スピード・分解能・測定項目において拡張:

システム分解能10倍、解析速度 3-10倍

- 200Vまでの高電圧,および 0.1nA までの微⼩な電流に対応

- 測定下限周波数 0.03Hz を実現

- システム分解能 <1×10-27A2/Hz

- インピーダンスマッチング範囲 10-10MΩ・MOSFET(FinFET, FD-SOI), BJT, JFET, ダイオード,抵抗,ICに対応

NoiseProPlus

- 9812DX/D/B/A および 主要IVメータをサポート

- Cascade/SUSS/MPI /HiSOL社のプローブステーションに対応

- マルチモード/マルチデバイス/マルチバイアスの自動測定をサポート

- 1/f RTN 雑⾳の同時解析

- 統計雑音モデル抽出・解析可能

■適用範囲

- テクノロジ開発におけるプロセス品質モニタリング

- Spice モデルパラメータ抽出における雑音解析

- 先端回路設計におけるプロセス/デバイス評価

SystemVerilog 設計・検証環境

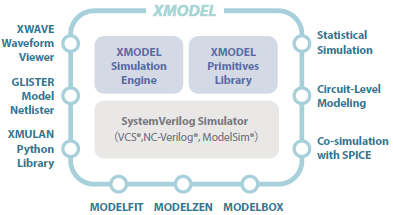

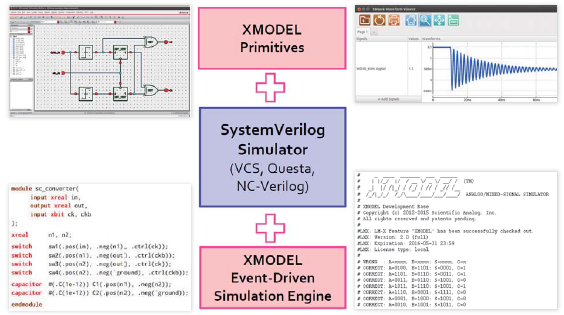

XMODEL

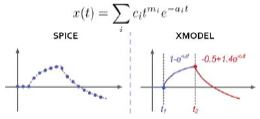

アナログ回路のVerilog モデルを生成

SystemVerilog シミュレータでアナログ回路をシミュレーション可能

ミックスドシグナル回路・チップ全体の設計・検証を高速化

■製品構成

- XMODEL コアシミュレータ:Verilogシミュレータ上で、XMODELのSystemVerilogモデルを用いた シミュレーションを実⾏するエンジン

- GLISTER:XMODELをVirtuoso®上で実行するための回路図生成・シミュレーション統合環境

- MODELZEN:回路図からSystemVerilogで動作するモデルを生成するツール

■ 特長

- 回路応答特性を関数記述として、連続的な波形を表現・イベントドリブンシミュレーションによる⾼速化

■対応SystemVerilog シミュレータ

- VCS®

- NC-Verilog®

- ModelSim®

■全体構成

■関連記事

- 2024年12月25日 製品情報 SX-Meister V18.0 リリースのお知らせ

- 2024年7月10日 ウェビナー&セミナー 「JEDAT Solution Seminar 2024」開催のご案内

- 2024年6月28日 製品情報 SX-Meister V17.0 リリースのお知らせ

- 2024年6月26日 ウェビナー&セミナー JEDATウェビナー 「JEDAT製品紹介セミナー」 開催のご案内

- 2023年8月1日 製品情報 PRIMARIUS TECHNOLOGIES社が回路シミュレータNanoSpice(TM)をバージョンアップ(バージョン2023.1)

- 2022年1月13日 お知らせ NanoSpiceTMが、Samsung Foundry 8nm Process Technologyの認証を取得

- 2021年12月5日 リソース White Paper

- 2021年11月26日 お知らせ ジーダット、パワーデバイス向け自動レイアウトツールを発売

Download

Download